# University of California, Santa Barbara

Department of Electrical and Computer Engineering

ECE 152A – Digital Design Principles

Final Exam – Solution August 29, 2007

| Name                   |

|------------------------|

| Perm #                 |

| Lab Section            |

|                        |

| Problem #1 (25 points) |

| Problem #2 (25 points) |

| Problem #3 (25 points) |

| Problem #4 (25 points) |

| Total (100 points)     |

- This is a 75 minute exam; closed book, closed notes, no calculators.

- Answer all questions on the exam.

#### Problem #1.

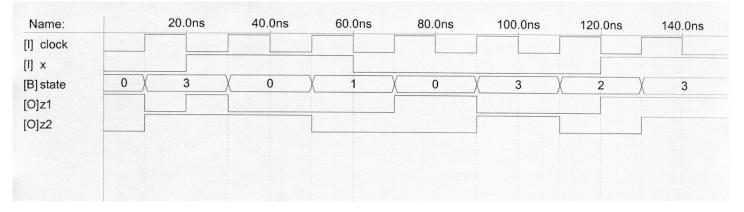

Complete the functional (zero delay) timing diagram below for the circuit realized by the following Verilog code:

```

module final (clock,x,z1,z2);

input clock,x;

output z1,z2;

wire z1;

reg z2;

reg [1:0]state;

assign z1 = x & state[1] | ~x & ~state[1] & ~state[0];

always @ (posedge clock)

begin

if(x)

state <= state + 1;

else

state <= state - 1;

z2 <= x & state[1] | ~x & ~state[1] & ~state[0];

end

```

endmodule

| Name:              | 20.0ns | 40.0ns | 60.0ns | 80.0ns | 100.0ns | 120.0ns | 140.0ns |

|--------------------|--------|--------|--------|--------|---------|---------|---------|

| [l] clock<br>[l] x |        |        |        |        |         |         |         |

| STATE = -          | 0 × 3  |        |        |        |         |         |         |

| 21 =               |        |        |        |        |         |         |         |

| 22 =               | 0      |        |        |        |         |         |         |

|                    |        |        |        |        |         |         |         |

Simulation output

7 points for state 9 points for z1 output 9 points for z2 output

## Problem #2.

In this problem, you are to design a portion of the controller for a high definition, hard disk, digital video recorder.

The controller receives four inputs from the remote control:

Play/Pause (PP),

- When playing (1X), causes video to be frozen

- Otherwise, causes playing to resume

Fast Forward (FF)

- Causes video to fast forward at 2X speed

- When fast forwarding, causes video to fast forward at 4X speed Rewind (RW)

- Causes video to rewind at 2X speed

- When rewinding, causes video to rewind at 4X speed Live (LV)

- Sets video source to live television

You can assume that only one button can be pressed at any time. You can also assume that if the hard disk is rewound to the beginning, it will automatically begin playing from that point and if the hard disk is fast forwarded to the end, it will revert to playing live television.

There are four output bits from the controller:

```

Play from disk (PFD)

```

- 0 = live television, 1 = hard disk

- Mode (MOD1, MOD0)

• 0 = continuous (1X speed), 1 = 2X speed, 2 = 4X speed, 3 = freeze Direction (DIR)

• 0 = forward, 1 = reverse

The 2X speed and 4X speed outputs are used for regular speed and high speed fast forward and fast reverse playing from the hard disk.

Note that only a small number of input and output combinations are actually valid. For instance, although there are four buttons on the remote control, there are only 5 (not 16) valid input combinations since, at most, one button can be active at any time. On the output side, for example, it is not possible to watch live television in reverse at high speed (viewing in reverse must come from video stored on the hard disk).

1. (10 points) Identify and describe all valid (and invalid) output combinations.

MODE DIR PFD LIVE, CONT, FORWARD × X MUST BE X PLAYED FROM DISK X X -× -DISK, CONT. FORWARD X - DISK, CONT, REVERSE (NOT IN SPEC) DISK, FAST FORWARD (2X) DISK, FAST REVERSE (2x) DISK, FAST FORWARD (4x) DISK, FAST REVERSE (4x) D FREE ZE 7 VALID STATES

(15 points) Based on the valid output combinations identified in part 1 above and all possible input combinations, construct a <u>state table</u> for the Moore machine implementing the controller. Use symbolic state names such as FRZ, FF2X, PLV, etc. on the state table and be sure the operation of your machine is clear.

| 0                                | UTPUT STATE                         | 5                              |                                    |                              |                          |

|----------------------------------|-------------------------------------|--------------------------------|------------------------------------|------------------------------|--------------------------|

|                                  | MODE                                | DIR                            | SYMPEO                             | uc Sta                       | TE                       |

| 0                                | 00                                  | 0                              | PLAY LI                            | $v \in = PL$                 | V                        |

| 1                                | 00                                  | 0                              |                                    | sk = Pli                     |                          |

| 1                                | 01                                  | 0                              | FF2X                               |                              |                          |

| 1                                | 01                                  | 1                              | RWZX                               |                              |                          |

| 1                                | 10                                  | 0                              | FF4X                               |                              |                          |

| 1                                | 10                                  | 1                              | RW4X                               |                              |                          |

| 1                                | 1 1                                 | 0                              | FRZ                                |                              |                          |

| STATE .                          | TABLE                               |                                |                                    |                              |                          |

| STATE -                          | TABLE                               |                                | NS                                 |                              |                          |

| STATE .                          | TABLE                               | PP                             | NS                                 | RW                           | LV                       |

|                                  |                                     |                                |                                    | RW V<br>RWZX                 |                          |

| PS                               | NULL                                | PP                             | FFF                                |                              | PLV                      |

| PS<br>PLV                        | NULL<br>PLV                         | PP<br>FRZ                      | PEFF 4                             | RWZX                         | PLV                      |

| PS<br>PLV<br>PLD                 | NULL<br>PLV<br>PLD                  | PP<br>FRZ<br>FRZ               | PEFF 11<br>PLV<br>FF2X             | RWZX<br>RWZX                 | PLV<br>PLV               |

| PS<br>PLV<br>PLD<br>FF2X         | NULL<br>PLV<br>PLD<br>FF2X          | PP<br>FRZ<br>FRZ<br>PLD        | PLV<br>PLV<br>FF2X<br>FF4X         | RWZX<br>RWZX<br>RWZX         | ,                        |

| PS<br>PLV<br>PLD<br>FF2X<br>RWZX | NULL<br>PLV<br>PLD<br>FF2X<br>RaJ2X | PP<br>FRZ<br>FRZ<br>PLD<br>PLD | PLV<br>PLV<br>FF2X<br>FF4X<br>FF2X | RWZX<br>RWZX<br>RWZX<br>RWYX | PLV<br>PLV<br>PLV<br>PLV |

#### Problem #3.

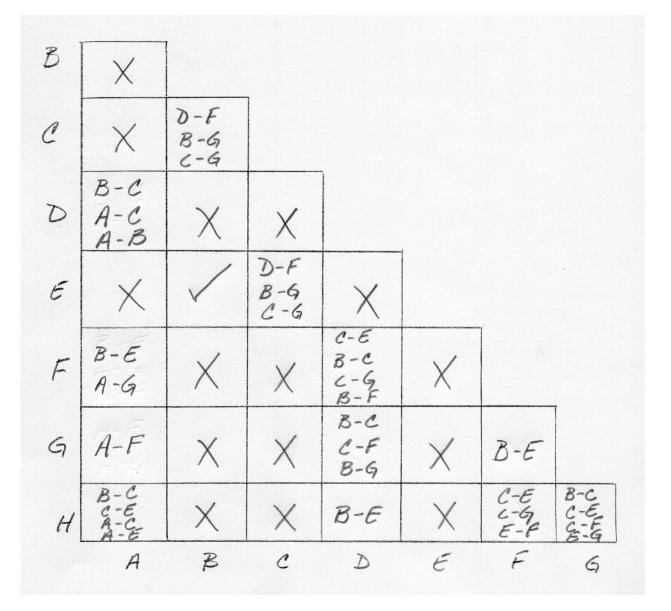

1. (10 points) For the state table given below, complete the implication table on the following page, illustrating its contents after the first and second passes. <u>Do not</u> include same state pairs or self-implied pairs in the implication table.

| NS, input = xy |   |      |                  |      |  |   |  |  |

|----------------|---|------|------------------|------|--|---|--|--|

| PS             | ( | 0 00 | 1 1 <sup>7</sup> | 1 10 |  | z |  |  |

|                |   |      |                  |      |  |   |  |  |

| A              |   | 3 C  | A                | A    |  | 0 |  |  |

| В              |   | = D  | В                | С    |  | 1 |  |  |

| С              |   | D C  | G                | G    |  | 1 |  |  |

| D              |   | С В  | С                | В    |  | 0 |  |  |

| Е              |   | = D  | В                | С    |  | 1 |  |  |

| F              |   | E C  | G                | F    |  | 0 |  |  |

| G              |   | з C  | F                | G    |  | 0 |  |  |

| Н              | ( | C E  | С                | Е    |  | 0 |  |  |

Final Exam Solution – Page 8 of 19

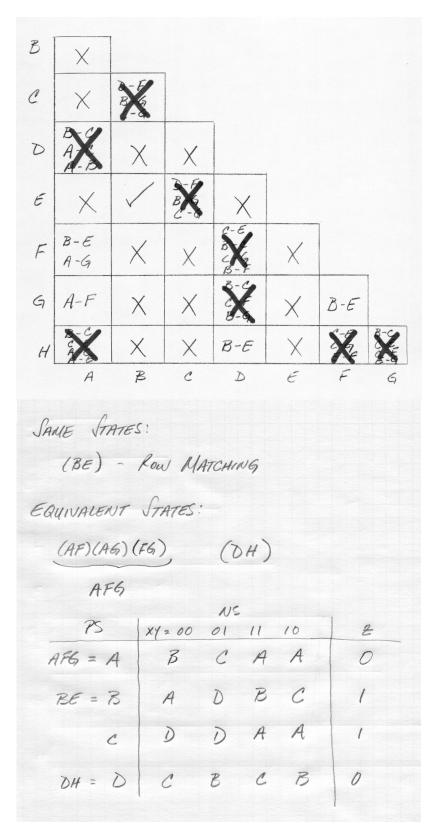

2. (5 points) Identify all (1) same states and (2) equivalent states and construct the reduced (simplified) state diagram.

3. (10 points) Verify your answer above by finding the equivalence partition using the Moore reduction procedure.

Po=(ABCDEFGH) P, = (ADFGH)(BCE) B(2) C(2)  $A \rightarrow c(z) \qquad D \rightarrow B(z)$ A(1) C(2) 3(2) A(1) C (2) E(2) B(2) $F \rightarrow c(2) \qquad G \rightarrow c(2) \qquad H \rightarrow E(2)$  $G(1) \qquad F(1) \qquad c(2)$ F(I)G(1) E(2) F (1) D (1) F (1)  $B \rightarrow D(I) \quad C \rightarrow D(I) \quad E \rightarrow D(I)$ B (2) B (2) G (I) C (2) C (2) G (1)

8/29/2007

#### Problem #4.

The truth table for the multiplication of one-bit binary numbers is shown below:

| Х | Y |   | XY |

|---|---|---|----|

| 0 | 0 |   | 0  |

| 0 | 1 | Í | 0  |

| 1 | 0 | Í | 0  |

| 1 | 1 | Í | 1  |

Obviously, the truth table above is also that of a 2-input AND gate.

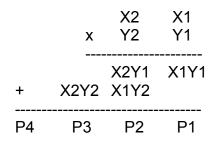

Like the multiplication of decimal numbers, multiplication of multiple-bit, unsigned binary numbers can be accomplished by generating the necessary partial products and adding them as shown below for the two-bit case.

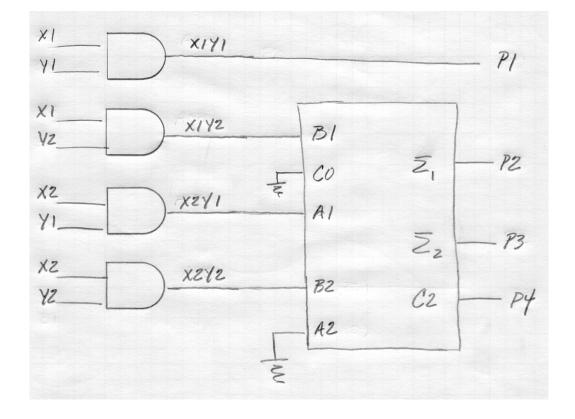

The multiplication of 2, 2-bit binary numbers results in a 4-bit product. Product bit P1 is partial product X1Y1 (as in the truth table above). Product bit P2 is the sum of partial products X2Y1 and X1Y2. Product bit P3 is the sum of partial product X2Y2 and any carry generated in the creation of P2. Product bit P4 is simply any carry generated in the creation of P3.

This type of binary multiplier is know as an "array multiplier" and can be expanded to any number of bits.

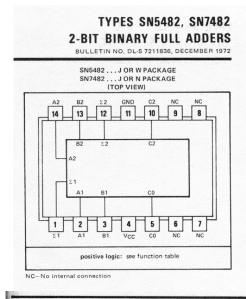

1. (5 points) Partial data sheets for the 7408 quad, 2-input AND gate and 7482 2-bit, binary full adder are given below. Using only these two devices (as many as necessary), construct the schematic diagram for a 2-bit array multiplier. Show all signal connections (i.e., no "floating inputs").

### 7408 Data Sheet

| QUADRUPLE 2-INPUT<br>POSITIVE-AND GATES |                                                                                                  |

|-----------------------------------------|--------------------------------------------------------------------------------------------------|

| 08                                      |                                                                                                  |

| positive logic:<br>Y = AB               |                                                                                                  |

| See page 6-10                           | SN5408 (J, W) SN7408 (J, N)<br>SN54LS08 (J, W) SN74LS08 (J, N)<br>SN54S08 (J, W) SN74LS08 (J, N) |

|                                         |                                                                                                  |

switching characteristics at V<sub>CC</sub> = 5 V, T<sub>A</sub> =  $25^{\circ}$ C

| ТҮРЕ                  | TEST<br>CONDITIONS#                            |     | tpLH (ns)<br>agation delay<br>o-high-level c |     | tpHL (ns)<br>Propagation delay time,<br>high-to-low-level output |     |     |  |

|-----------------------|------------------------------------------------|-----|----------------------------------------------|-----|------------------------------------------------------------------|-----|-----|--|

|                       |                                                | MIN | TYP                                          | MAX | MIN                                                              | TYP | MAX |  |

| '08                   | $C_{L} = 15  pF$ , $R_{L} = 400  \Omega$       |     | 17.5                                         | 27  |                                                                  | 12  | 19  |  |

| 'H11, 'H21            | C <sub>L</sub> = 25 pF, R <sub>L</sub> = 280 Ω |     | 7.6                                          | 12  |                                                                  | 8.8 | 12  |  |

| 'LS08, 'LS11<br>'LS21 | $C_L = 15  pF$ , $R_L = 2  k\Omega$            |     | 8                                            | 15  |                                                                  | 10  | 20  |  |

| 1000 1011             | $C_{L} = 15  pF$ , $R_{L} = 280  \Omega$       |     | 4.5                                          | 7   |                                                                  | 5   | 7.5 |  |

| 'S08, 'S11            | $C_{L} = 50  pF, R_{L} = 280  \Omega$          |     | 6                                            |     |                                                                  | 7.5 |     |  |

$^{\#}\mathrm{Load}$  circuit and voltage waveforms are shown on pages 3-10 and 3-11.

## 7482 Data Sheet

|       | INP | UTS |    | -                   | -  | OUT                 | PUTS |    |       |  |

|-------|-----|-----|----|---------------------|----|---------------------|------|----|-------|--|

| 6. A. |     |     |    | WHEN CO = L WHEN CO |    | WHEN CO = L WHEN CO |      |    | 0 = H |  |

| A1    | B1  | A2  | B2 | Σ1                  | Σ2 | C2                  | Σ1   | Σ2 | C2    |  |

| L     | L   | L   | L  | L                   | L  | L                   | н    | L  | L     |  |

| н     | L   | L   | L  | н                   | L  | L                   | L    | н  | L     |  |

| L     | н   | L   | L  | н                   | L  | L                   | L    | н  | L     |  |

| н     | н   | L   | L  | L                   | н  | L                   | н    | н  | L     |  |

| L     | L   | н   | L  | L                   | н  | L                   | н    | н  | L     |  |

| н     | L   | н   | L  | н                   | н  | L                   | L    | L  | н     |  |

| L     | н   | н   | L  | H                   | н  | L                   | L    | L  | н     |  |

| н     | н   | н   | L  | L                   | L  | н                   | H    | L  | н     |  |

| L     | L   | L   | н  | L                   | н  | L                   | Н    | н  | L     |  |

| н     | L   | L   | н  | н                   | н  | L                   | L    | L  | н     |  |

| L     | н   | L   | н  | н                   | н  | L                   | L    | L  | н     |  |

| н     | н   | L   | н  | L                   | L  | н                   | н    | L  | н     |  |

| L     | L   | н   | н  | L                   | L  | н                   | н    | L  | н     |  |

| н     | L   | н   | н  | н                   | L  | н                   | L    | н  | н     |  |

| L     | н   | н   | н  | H                   | L  | н                   | L    | н  | н     |  |

| н     | н   | н   | н  | L                   | н  | н                   | H    | н  | н     |  |

| PARAMETER        | FROM<br>(INPUT) | TO<br>(OUTPUT) | TEST CONDITIONS                          | MIN TYP | мах | UNIT |  |

|------------------|-----------------|----------------|------------------------------------------|---------|-----|------|--|

| tPLH             | CO              | Σ1             |                                          |         | 34  | ns   |  |

| <sup>t</sup> PHL | CU              | 21             |                                          |         | 40  |      |  |

| tPLH             | B2              | Σ2             | $C_{L} = 15  pF$ , $R_{L} = 400  \Omega$ | 40      |     |      |  |

| <b>tPHL</b>      | 02              |                | CL - IS PF, INC 100 IS                   |         | 35  | ns   |  |

| tPLH .           | CO              | Σ2             |                                          |         | 38  | ns   |  |

| <sup>t</sup> PHL | 00              |                |                                          |         | 42  |      |  |

| tPLH             | CO              | C2             | C. = 15 = 5 . = 700 O                    | 12      | 19  | ns   |  |

| tPHL .           | 00              | 02             | $C_L = 15 \text{ pF}, R_L = 780 \Omega$  | 17      | 27  |      |  |

${}^{i}_{t_{bLH}}$  ≡ propagation delay time, low-to-high-level output  ${}^{i}_{pHL}$  ≡ propagation delay time, high-to-low-lavel output NOTE 4: Load circuit and voltage waveforms are shown on page 3-10.

2. (5 points) What is the critical path and maximum propagation delay through the array multiplier and what input conditions are necessary to produce the maximum propagation delay?

Use the specifications for the type '08 device (not the 'LS08 or 'S08) and note that the 7482 delays from A2 to Sum2 are the same as the B2 to Sum2 delays given on the data sheet.

7408:

$$t_{PLH} = 27nS$$

,  $t_{PHL} = 19nS$

7482: Since Co IS ALWAYS EERO

MAX DELAY IS  $BZ \rightarrow ZZ'$

$t_{PLH} = 40nS$ ,  $t_{PHL} = 35nS$

CRITICAL PATH

$XZ(OLYZ) \rightarrow 7408 t_{PLH} \rightarrow BZ$

$\rightarrow 748Z(BZ \rightarrow ZZ) t_{PLH} \rightarrow ZZ$

$= 27nS + 40nS = 67nS$

TO CAUSE ZZ TO GO HIGH WHEN BZ GOES

HIGH, TUTELNAL CALLY OI HUST BE LOW...

SINCE CO IS ALWAYS EERO, XI AND YI MUST

NOT BE II..... XZ AND YZ MUST BE

HIGH FOL INPUT BZ TO GO HIGH...

INPUT CONDITIONS:  $XZX, YZY,$

$YZYZ = 11, X,Y,  $\pm 11 \rightarrow 10$

$11$

$10$$

Final Exam Solution – Page 15 of 19

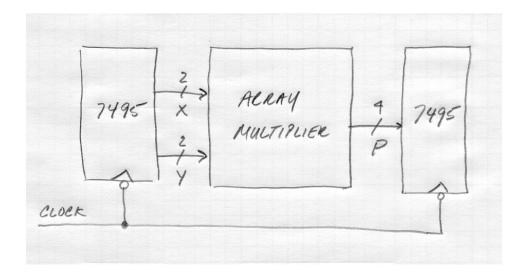

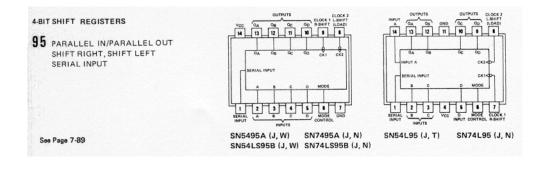

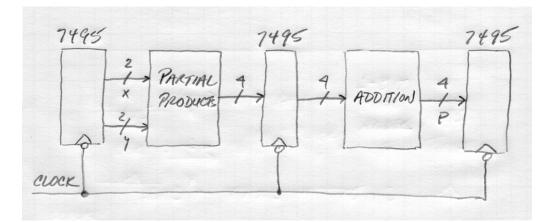

3. (5 points) We now want to add registers for the inputs and outputs of the array multiplier. On each falling clock edge, two new operands will be loaded on the input side and the result of the previous multiplication will be loaded on the output side. Partial specs for the 7495, 4-bit shift register are given on the following page.

As is often the case, the register has more functionality than we need (the shift capability) so it will be configured to operate in parallel input/output mode only. The mode control input will be held high making the SERIAL INPUT and CLOCK1 inputs don't cares. On each falling CLOCK2 edge, inputs A through D will be loaded into the register.

If 7495 registers are added to the inputs and outputs as shown below, what is the minimum clock period necessary to insure correct operation?

MINIMUM CLOCK PERIOD: CLK -> Q + COMBO LOGIC + SETUP TIME 32ns + 67ns + 15ns = 114n5

## 7495 Data Sheet

|         |        |       | 1      | FUNC     | TION | TABL | E |     |     |                 |     |

|---------|--------|-------|--------|----------|------|------|---|-----|-----|-----------------|-----|

|         |        |       | INPUTS |          |      |      |   |     | OUT | PUTS            |     |

| MODE    | CLOCKS |       | SERIAL | PARALLEL |      |      |   |     |     |                 |     |

| CONTROL | 2 (L)  | 1 (R) | SERIAL | A        | В    | С    | D | QA. | QB  | ac              | QD  |

| н       | н      | х     | х      | x        | х    | х    | х | QAO | QBO | Q <sub>C0</sub> | QDO |

| н       | ţ      | х     | x      | а        | b    | с    | d | a   | b   | c               | d   |

|                                                              |     | SN5495 | A    | SN7495A |     |      |      |

|--------------------------------------------------------------|-----|--------|------|---------|-----|------|------|

|                                                              | MIN | NOM    | MAX  | MIN     | NOM | MAX  | UNIT |

| Supply voltage, VCC                                          | 4.5 | 5      | 5.5  | 4.75    | 5   | 5.25 | V    |

| High-level output current, IOH                               |     |        | -800 |         |     | -800 | μA   |

| Low-level output current, IOL                                |     |        | 16   |         |     | 16   | mA   |

| Clock frequency, fclock                                      | 0   |        | 25   | 0       |     | 25   | MHz  |

| Width of clock pulse, tw(clock) (see Figure 1)               | 20  |        |      | 20      |     |      | ns   |

| Setup time, high-level or low-level data, tsu (see Figure 1) | 15  |        |      | 15      |     |      | ns   |

| Hold time, high-level or low-level data, th (see Figure 1)   | 0   |        |      | 0       |     |      | ns   |

| Time to enable clock 1, tenable 1 (see Figure 2)             | 15  |        |      | 15      |     |      | ns   |

| Time to enable clock 2, tenable 2 (see Figure 2)             | 15  |        |      | 15      |     |      | ns   |

| Time to inhibit clock 1, tinhibit 1 (see Figure 2)           | 5   |        |      | 5       |     |      | ns   |

| Time to inhibit clock 2, tinhibit 2 (see Figure 2)           | 5   |        |      | 5       |     |      | ns   |

| Operating free-air temperature, TA                           | -55 |        | 125  | 0       |     | 70   | °C   |

| switching  | characteristics,    | Vcc = | 5 V. | T۸  | = 25° C |

|------------|---------------------|-------|------|-----|---------|

| N. Hilling | ondiana ocorrocios, | VUL I | υv,  | · A | 20 0    |

|      | PARAMETER                                                   | TEST CONDITIONS                                                                                         | MIN | TYP | MAX | UNIT |

|------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| fmax | Maximum clock frequency                                     | C. = 15 = 5                                                                                             | 25  | 36  |     | MHz  |

| PLH  | Propagation delay time, low-to-high-level output from clock | $\begin{array}{c} C_L = 15  \text{pF},  \text{R}_L = 400  \Omega, \\ See \ \text{Figure 1} \end{array}$ |     | 18  | 27  | ns   |

| PHL  | Propagation delay time, high-to-low-level output from clock |                                                                                                         |     | 21  | 32  | ns   |

4. (5 points) One method of increasing clock frequency (at the cost of latency) is via pipelining. In a pipelined design, the combinational processing is broken up into pipeline stages with registers between each of the stages. For our array multiplier, we can break up the multiplication into partial product generation and addition as shown in the generic block diagram below:

What is the minimum clock period for the 2-stage pipelined implementation of the synchronous, array multiplier?

PARTIAL PRODUCT CONTEINATIONAL DELAY 7408: tpin = 27ns, tpin = 19ns ADDITION CONBINATIONAL DELAY 7482 (82-722): tPLH = 40nS, tPHL = 35nS MUST USE GREATEST CONTEINATIONAL DECAY CLK -> Q + COMBO LOGK + SETUP TIME 32ns + 40ns + 15ns = 87 nS

Final Exam Solution – Page 18 of 19

5. (5 points) For the implementations in parts 3 and 4 above, assume that on the first falling clock edge the first two operands are loaded, on the second falling clock edge the second operands are loaded, on the third the third, etc.

If the first two operands are loaded at time = 0, when is the first product available for (a) the non-pipelined version and (b) the pipelined version?

At what point (after how many products are generated) does the pipelined design yield a performance advantage (more products in less time)?

|                                                                                                                                                                                                                                               | NON - PIPELINED | PIPELINED   |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------|--|--|--|--|

| 1                                                                                                                                                                                                                                             | 114 ns          | 87x2= 174n5 |  |  |  |  |

| 2                                                                                                                                                                                                                                             | 228nS           | 261nS       |  |  |  |  |

| 3                                                                                                                                                                                                                                             | 342n S          | 34815       |  |  |  |  |

| 4                                                                                                                                                                                                                                             | 45605           | 435ns       |  |  |  |  |

| THE NON-PIPEINES DESIGN PRODUCES THE<br>FIRST PRODUCT AFTER ONE CLOCK PELIOD,<br>114 ns THE PIPEINED DESIGN REQUIRES<br>TWO CLOCK PERIODS FOR THE PIPEST PRODUCT,<br>174ns AFTER THAT BOTH DESIGNS GENERATE<br>A PRODUCT ON EACH CLICK PERIOD |                 |             |  |  |  |  |